kolondrej, не прокатит ) Да, синхросигнал укоротится, но появится ещё один лишний импульс, что приведет к срыву картинки, плюс строка сместится в сторону от центра, т.е. рисунок будет сдвинут.

Alexander, для доработки «Нафани» я чертил схему в «Eagle CAD» (это софт для черчения схем и создания плат).

А для симуляции можно использовать, например, «Icarus Verilog» (http://iverilog.icarus.com/) + «GTKWave» (http://gtkwave.sourceforge.net/).

Вся стандартная TTL-логика давно описана на Verilog HDL (язык, используемый для описания и моделирования электронных систем). Найти исходники можно в сети на разных ресурсах, но наиболее полная коллекция логики серий 74xx есть в библиотеке maxplus2 программы «Quartus II 13». В этой программе можно схемку начертить, а потом экспортировать в Verilog HDL, хотя лучше и правильней всю основную логику прописывать вручную, т.к. после экспорта код всё равно придется править в большинстве случаев. Ну, а исходники нужных чипов логики можно из «Quartus'а» экспортировать по отдельности.

Сопоставить отечественную маркировку с импортной можно по справочникам, например:

http://rfanat.qrz.ru/s21/ms_74xx.html

На практике это выглядит так. Мы можем, например, быстро и легко сделать симуляцию тактового генератора и получить сигналы: TI, RAS, H0, H1, H2, H3. Нам понадобится для этого всего два элемента: ТМ2 (7474.v) и ИЕ7 (74193.v).

Создать нам надо будет четыре файла:

leningrad.v – это будет часть тактового генератора «Ленинграда»

leningrad_tb.v - test bench (файл, в котором описаны параметры симуляции)

7474.v – триггер ТМ2

74193.v – счетчик ИЕ7

-----------------------------------------

// Файл leningrad.v

module leningrad(

CLK,

VCC,

GND

);

// Входные сигналы: CLK = 14 МГц, VCC = 1, GND = 0

input wire CLK;

input wire VCC;

input wire GND;

wire H0;

wire H1;

wire H2;

wire H3;

wire TI;

wire TI_inv;

wire RAS;

wire RAS_inv;

ttl_7474 D2(

.n1CLK(CLK),

.n1D(TI_inv),

.n1PRN(VCC),

.n1CLRN(VCC),

.n1Q(TI),

.n1QN(TI_inv),

.n2CLK(TI),

.n2D(H0),

.n2PRN(VCC),

.n2CLRN(VCC),

.n2Q(RAS_inv),

.n2QN(RAS));

wire [3:0] H;

wire [3:0] P = 4'b1111;

counter_74193 D3(.clr(GND),.up(TI_inv),.load_n(VCC),.P(P),.Q(H));

assign H0 = H[0];

assign H1 = H[1];

assign H2 = H[2];

assign H3 = H[3];

endmodule

-----------------------------------------

// Файл leningrad_tb.v

`timescale 1 ns / 100 ps

module leningrad_tb;

reg CLK, VCC=1, GND=0;

leningrad LENINGRAD (.CLK(CLK),.VCC(VCC),.GND(GND));

// Период в наносекундах. Для 14 МГц, период будет равен: 1000/14=71,42

always #71 begin

CLK =~ CLK;

end

initial begin

CLK=0;

// Длительность симуляции в наносекундах

#7100 $finish;

end

// Полный дамп результатов симуляции

initial begin

$dumpfile("leningrad_tb.vcd");

$dumpvars(0,leningrad_tb);

end

endmodule

-----------------------------------------

// Файл 7474.v

// Purpose: D flip-flop

// Western: SN74LS74

// USSR: K555TM2/К555ТМ2

module ttl_7474 (

n2CLRN,

n2CLK,

n2D,

n2PRN,

n1CLRN,

n1CLK,

n1D,

n1PRN,

n1Q,

n1QN,

n2Q,

n2QN

);

input wire n2CLRN;

input wire n2CLK;

input wire n2D;

input wire n2PRN;

input wire n1CLRN;

input wire n1CLK;

input wire n1D;

input wire n1PRN;

output wire n1Q;

output wire n1QN;

output wire n2Q;

output wire n2QN;

reg DFF_10=0;

reg DFF_9=0;

assign n1Q = DFF_9;

assign n2Q = DFF_10;

always@(posedge n2CLK or negedge n2CLRN or negedge n2PRN)

begin

if (!n2CLRN)

begin

DFF_10 <= 0;

end

else

if (!n2PRN)

begin

DFF_10 <= 1;

end

else

begin

DFF_10 <= n2D;

end

end

assign n2QN = ~DFF_10;

assign n1QN = ~DFF_9;

always@(posedge n1CLK or negedge n1CLRN or negedge n1PRN)

begin

if (!n1CLRN)

begin

DFF_9 <= 0;

end

else

if (!n1PRN)

begin

DFF_9 <= 1;

end

else

begin

DFF_9 <= n1D;

end

end

endmodule

-----------------------------------------

// Файл 74193.v

// Purpose: Presettable 4-bit binary up/down counter

// Western: SN74LS193

// USSR: 555IE7/555ИЕ7

module counter_74193

(

input clr,

input up,

input down,

input load_n, // Initial counter value load strobe

input [3:0] P, // 4-bit parallel input

output co_n, // Carry-out

output bo_n, // Borrow-our

output [3:0] Q

);

reg co = 1'b0;

reg bo = 1'b0;

reg [3:0] count = 0;

always @(posedge clr or negedge load_n or posedge up or posedge down)

begin

if (clr)

begin

count <= 4'b0000;

co <= 1'b0;

bo <= 1'b0;

end

else if (~load_n)

count <= P;

else if (up)

begin

count <= count + 1;

// Set carry-out flag when counted till 14 ('b1110) and up is active (high)

co <= ~count[0] & count[1] & count[2] & count[3] & up;

bo <= 1'b0;

end

else if (down)

begin

count <= count - 1;

co <= 1'b0;

// Set borrow out flag when counted till 1 ('b0001) and down is active (high)

bo <= ~(~count[0] | count[1] | count[2] | count[3]) & down;

end

end

assign Q = count;

assign co_n = ~co;

assign bo_n = ~bo;

endmodule

-----------------------------------------

Компилируем так (на Linux):

iverilog -o leningrad_tb -s leningrad_tb *.v

vvp leningrad_tb

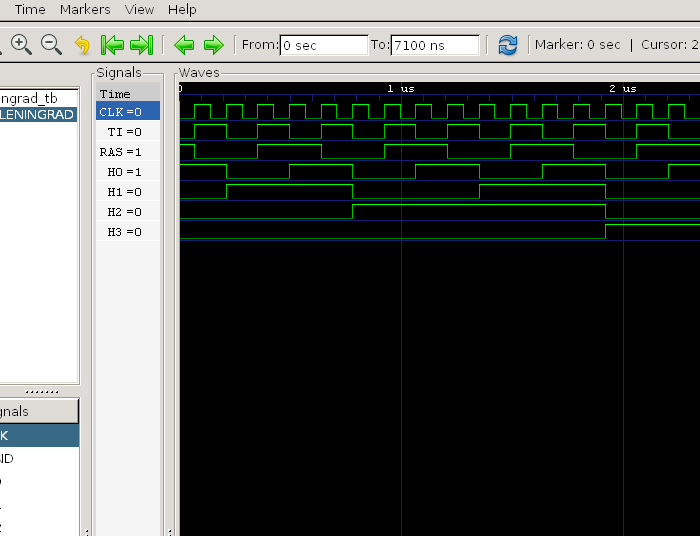

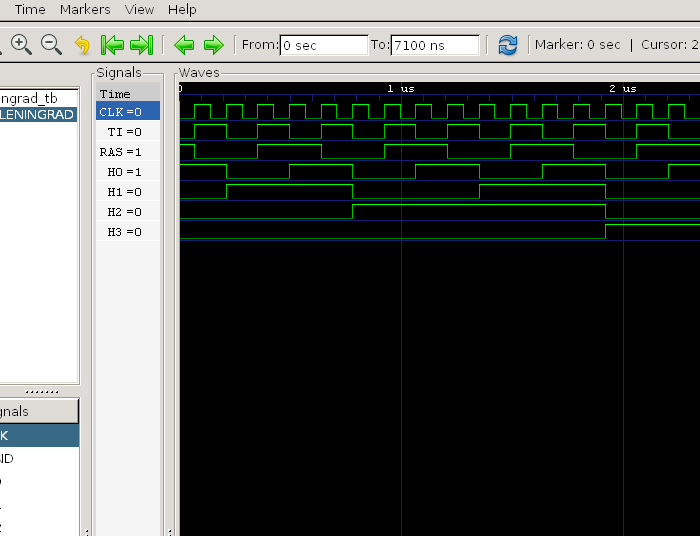

Полученный файл leningrad_tb.vcd открываем программой GTKWave:

Теперь мы видим, что

1. TI = CLK/2 = 14/2= 7 МГц

2. RAS = TI/2 = 7/2 = 3,5 МГц

3. H0 = 3,5 МГц (смещен относительно RAS)

4. H1 = 1,75 МГц (отсюда берут тактовый сигнал для AY-3-8910)

5. H2 = 875 КГц

6. H3 = 437,5 КГц

В сети есть и исходник процессора Z80 на Verilog HDL, так что можно так и весь «Ленинград» сэмулировать. Будут, правда, некоторые сложности с правильной эмуляцией сигнала INT, но и это при желании возможно.

Alexander, для доработки «Нафани» я чертил схему в «Eagle CAD» (это софт для черчения схем и создания плат).

А для симуляции можно использовать, например, «Icarus Verilog» (http://iverilog.icarus.com/) + «GTKWave» (http://gtkwave.sourceforge.net/).

Вся стандартная TTL-логика давно описана на Verilog HDL (язык, используемый для описания и моделирования электронных систем). Найти исходники можно в сети на разных ресурсах, но наиболее полная коллекция логики серий 74xx есть в библиотеке maxplus2 программы «Quartus II 13». В этой программе можно схемку начертить, а потом экспортировать в Verilog HDL, хотя лучше и правильней всю основную логику прописывать вручную, т.к. после экспорта код всё равно придется править в большинстве случаев. Ну, а исходники нужных чипов логики можно из «Quartus'а» экспортировать по отдельности.

Сопоставить отечественную маркировку с импортной можно по справочникам, например:

http://rfanat.qrz.ru/s21/ms_74xx.html

На практике это выглядит так. Мы можем, например, быстро и легко сделать симуляцию тактового генератора и получить сигналы: TI, RAS, H0, H1, H2, H3. Нам понадобится для этого всего два элемента: ТМ2 (7474.v) и ИЕ7 (74193.v).

Создать нам надо будет четыре файла:

leningrad.v – это будет часть тактового генератора «Ленинграда»

leningrad_tb.v - test bench (файл, в котором описаны параметры симуляции)

7474.v – триггер ТМ2

74193.v – счетчик ИЕ7

-----------------------------------------

// Файл leningrad.v

module leningrad(

CLK,

VCC,

GND

);

// Входные сигналы: CLK = 14 МГц, VCC = 1, GND = 0

input wire CLK;

input wire VCC;

input wire GND;

wire H0;

wire H1;

wire H2;

wire H3;

wire TI;

wire TI_inv;

wire RAS;

wire RAS_inv;

ttl_7474 D2(

.n1CLK(CLK),

.n1D(TI_inv),

.n1PRN(VCC),

.n1CLRN(VCC),

.n1Q(TI),

.n1QN(TI_inv),

.n2CLK(TI),

.n2D(H0),

.n2PRN(VCC),

.n2CLRN(VCC),

.n2Q(RAS_inv),

.n2QN(RAS));

wire [3:0] H;

wire [3:0] P = 4'b1111;

counter_74193 D3(.clr(GND),.up(TI_inv),.load_n(VCC),.P(P),.Q(H));

assign H0 = H[0];

assign H1 = H[1];

assign H2 = H[2];

assign H3 = H[3];

endmodule

-----------------------------------------

// Файл leningrad_tb.v

`timescale 1 ns / 100 ps

module leningrad_tb;

reg CLK, VCC=1, GND=0;

leningrad LENINGRAD (.CLK(CLK),.VCC(VCC),.GND(GND));

// Период в наносекундах. Для 14 МГц, период будет равен: 1000/14=71,42

always #71 begin

CLK =~ CLK;

end

initial begin

CLK=0;

// Длительность симуляции в наносекундах

#7100 $finish;

end

// Полный дамп результатов симуляции

initial begin

$dumpfile("leningrad_tb.vcd");

$dumpvars(0,leningrad_tb);

end

endmodule

-----------------------------------------

// Файл 7474.v

// Purpose: D flip-flop

// Western: SN74LS74

// USSR: K555TM2/К555ТМ2

module ttl_7474 (

n2CLRN,

n2CLK,

n2D,

n2PRN,

n1CLRN,

n1CLK,

n1D,

n1PRN,

n1Q,

n1QN,

n2Q,

n2QN

);

input wire n2CLRN;

input wire n2CLK;

input wire n2D;

input wire n2PRN;

input wire n1CLRN;

input wire n1CLK;

input wire n1D;

input wire n1PRN;

output wire n1Q;

output wire n1QN;

output wire n2Q;

output wire n2QN;

reg DFF_10=0;

reg DFF_9=0;

assign n1Q = DFF_9;

assign n2Q = DFF_10;

always@(posedge n2CLK or negedge n2CLRN or negedge n2PRN)

begin

if (!n2CLRN)

begin

DFF_10 <= 0;

end

else

if (!n2PRN)

begin

DFF_10 <= 1;

end

else

begin

DFF_10 <= n2D;

end

end

assign n2QN = ~DFF_10;

assign n1QN = ~DFF_9;

always@(posedge n1CLK or negedge n1CLRN or negedge n1PRN)

begin

if (!n1CLRN)

begin

DFF_9 <= 0;

end

else

if (!n1PRN)

begin

DFF_9 <= 1;

end

else

begin

DFF_9 <= n1D;

end

end

endmodule

-----------------------------------------

// Файл 74193.v

// Purpose: Presettable 4-bit binary up/down counter

// Western: SN74LS193

// USSR: 555IE7/555ИЕ7

module counter_74193

(

input clr,

input up,

input down,

input load_n, // Initial counter value load strobe

input [3:0] P, // 4-bit parallel input

output co_n, // Carry-out

output bo_n, // Borrow-our

output [3:0] Q

);

reg co = 1'b0;

reg bo = 1'b0;

reg [3:0] count = 0;

always @(posedge clr or negedge load_n or posedge up or posedge down)

begin

if (clr)

begin

count <= 4'b0000;

co <= 1'b0;

bo <= 1'b0;

end

else if (~load_n)

count <= P;

else if (up)

begin

count <= count + 1;

// Set carry-out flag when counted till 14 ('b1110) and up is active (high)

co <= ~count[0] & count[1] & count[2] & count[3] & up;

bo <= 1'b0;

end

else if (down)

begin

count <= count - 1;

co <= 1'b0;

// Set borrow out flag when counted till 1 ('b0001) and down is active (high)

bo <= ~(~count[0] | count[1] | count[2] | count[3]) & down;

end

end

assign Q = count;

assign co_n = ~co;

assign bo_n = ~bo;

endmodule

-----------------------------------------

Компилируем так (на Linux):

iverilog -o leningrad_tb -s leningrad_tb *.v

vvp leningrad_tb

Полученный файл leningrad_tb.vcd открываем программой GTKWave:

Теперь мы видим, что

1. TI = CLK/2 = 14/2= 7 МГц

2. RAS = TI/2 = 7/2 = 3,5 МГц

3. H0 = 3,5 МГц (смещен относительно RAS)

4. H1 = 1,75 МГц (отсюда берут тактовый сигнал для AY-3-8910)

5. H2 = 875 КГц

6. H3 = 437,5 КГц

В сети есть и исходник процессора Z80 на Verilog HDL, так что можно так и весь «Ленинград» сэмулировать. Будут, правда, некоторые сложности с правильной эмуляцией сигнала INT, но и это при желании возможно.

вторник, 25 февраля 15:50:12 2020